首页 > 快讯 科学家制备氧化锌薄膜晶体管环形振荡器,有望被引入先进芯片制造

科学家制备氧化锌薄膜晶体管环形振荡器,有望被引入先进芯片制造

在南方科技大学,有这样一位外籍老师——李毅达。他出生和成长于新加坡,甚至本科和博士也在那里完成,但他说得一口流利的中文。而且作为一名半导体领域的专家,他还拥有在台积电工作过的经历。

图 | 李毅达(来源:李毅达)

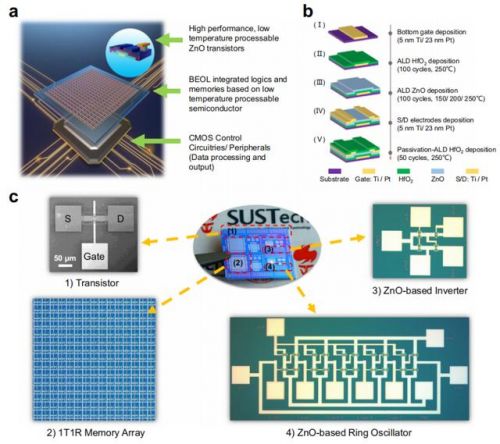

在南方科技大学,李毅达的主要研究方向是新型半导体材料器件。前不久,李毅达课题组和合作者通过优化原子层沉积(ALD,Atomic layer deposition)工艺参数、优化器件结构等,制备出一款氧化锌薄膜晶体管。

在目前的原子层沉积工艺上,该晶体管实现了最稳定、最可靠、以及最高的电子迁移率性能。在应用上:

这款晶体管在忆阻器存储阵列中可被作为驱动晶体管。研究中,该团队已经成功实现一个 32×32(1 kBit)的忆阻器存储阵列,其中氧化锌薄膜晶体管充当存储阵列的驱动晶体管。基于低温可制备的工艺,能够以三维堆叠的方式形成超高密度存储阵列。

同时,这款晶体管在互补金属氧化物半导体(CMOS,Complementary Metal Oxide Semiconductor)后端集成领域具有潜在的应用价值。由于这款晶体管不但性能稳定、可靠,而且能兼容 CMOS 后端工艺,故能为实现 CMOS 后端的集成电路提供参考。

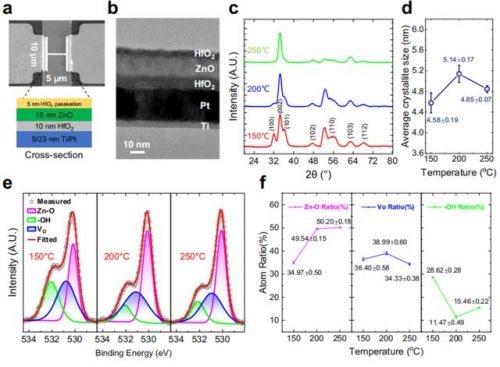

研究中,他们先是研究了基于氧化锌半导体的薄膜晶体管,通过大量的实验,开发了单个器件的制备工艺,做了大量的材料表征(例如 X 射线衍射、X 射线光电子能谱等)和电学表征工作,借此得到了稳定、可靠的高性能薄膜晶体管。

李毅达展望称:“我们相信再通过适当的工艺优化和验证,有望继续突破现有的性能,最终引入先进芯片工艺里。”

(来源:Nature Communications)

为何需要更好的氧化物薄膜晶体管?

在传统的冯诺依曼计算架构中,存储单元和计算单元是分开独立的。在数据处理和数据计算时,数据在存储单元和计算单元之间的交换过程,占据着绝大部分的时间和功耗。

随着数据驱动型应用例如大数据、物联网等需求的持续增长,传统的冯诺依曼架构面临着严重的挑战,这就是人们熟知的“冯诺依曼瓶颈”。

当使用传统方法提升芯片计算的性能时,无法避免器件的微缩和密度的增加。但是随着在摩尔定律下二维(2D)平面电路器件不断微缩并趋于极限,先进芯片的制造工艺面临着巨大的挑战。

通过进一步微缩器件来在 2D 平面上提高集成密度的方法遇到了难以逾越的技术瓶颈,限制了芯片计算性能提升的速度。

为了突破“冯诺依曼瓶颈”,学界在各种可能的方向进行了探索,其中在微电子产业一个主流的方向便是三维(3D)单片集成,即把逐层的逻辑电路、存储器件、传感器件堆叠在硅芯片之上,以构建出一个以存储为中心的计算系统,以此大幅节省芯片面积、提高集成密度。

在 3D 单片集成的主流研究之中,不可避免地要研发下一代可被低温制备的高性能半导体。同时,一些突破性进展也将对微电子产业带来颠覆性的改变,成为实现下一代计算芯片的关键。

与硅基晶体管相比,氧化物半导体具有诸多优势例如宽禁带、可以低温大面积生长、透明度好等,因此氧化物半导体在这些新型计算架构中具备潜在的应用价值。

近几年,新型氧化物半导体的研究取得了重大进步,以铟镓锌氧化物为代表的氧化物半导体已经广泛应用于有机发光二极管(OLED,organic light-emitting diode)和有源矩阵有机发光二极体(AMOLED,Active-matrix organic light-emitting diode)显示屏。

然而,氧化物半导体在其他领域比如边缘计算、存内计算、三维集成等领域的应用并未成熟,目前仍然面临一些挑战。

因此,实现性能良好、稳定、可靠的氧化物薄膜晶体管,对于拓宽其应用领域至关重要。以上便是李毅达开展本次课题的出发点所在。

(来源:Nature Communications)

“起早贪黑半个月做的样品,测不出任何数据”

据介绍,一开始课题组只打算利用新型的原子层沉积技术开发基于氧化锌半导体的薄膜晶体管。

历时半年左右,他们完成了各种半导体工艺的开发工作,比如光刻工艺、刻蚀工艺、镀膜工艺等等。通过优化各种工艺参数,确定可以满足相关工艺步骤和参数。

随后,他们对单个薄膜晶体管器件的进行大量表征,比如材料表征、电学表征等。

在完成单个薄膜晶体管的开发工作后,他们发现这种氧化锌薄膜晶体管有着很高的载流子迁移率、以及极大的工作电流(电流达到毫安级)。

于是,他们打算将这款薄膜晶体管集成到忆阻器的存储阵列中,在忆阻器 1T1R(One Transistor One Resistor)存储阵列中充当驱动晶体管,借此验证它的驱动能力。

然后,他们开始进行存储阵列的版图设计、工艺开发、加工制造,并进行了大量测试。实验结果证明,该薄膜晶体管能够轻松驱动忆阻器存储阵列的工作。

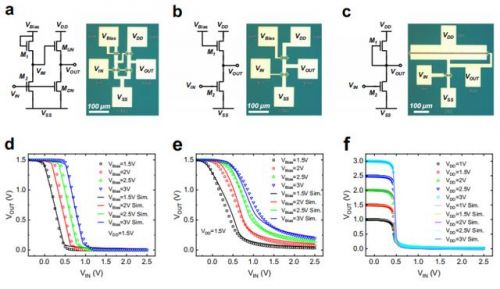

随后,为了进一步推动该薄膜晶体管在系统级别的应用,他们启动了单器件的建模和基本电路的验证工作。

基于大量的测试数据和物理分析,其又建立了氧化锌薄膜晶体管的 TCAD 紧凑模型(注:TCAD 的全称是 Technology Computer Aided Design,指半导体工艺模拟以及器件模拟工具)。

然后,在建立的紧凑模型的基础上,他们设计出不同种类的反相器和环形振荡器,以验证氧化锌薄膜晶体管在电路应用中的价值。

然后,基于该模型他们又设计了存储阵列、反相器和环形振荡器电路,实现了系统级的验证。

同时,该团队还全面分析和评估了单个器件,并拓展到电路应用层面例如环形振荡器电路。所有实验结果都充分证明了氧化锌薄膜晶体管在电路中的应用能力。

(来源:Nature Communications)

事实上在课题启动的最初三个月里,他们连续做了 4 批实验,结果统统失败了。每做一批实验样品需要 2 周时间,起早贪黑半个月做出来的样品,测不出任何数据,这让他们充满煎熬和挫败感。

李毅达说:“但是,科研工作还得继续。每一次实验失败后,我们都认真分析原因,仔细复盘每一步工艺步骤,回忆每一处细节,查缺补漏。直到三个月后,我们终于做出了可以工作的器件。”

虽然刚开始制备的器件性能比较差,但却实现了从 0 到 1 的突破,这让他们备受鼓舞。更加重要的是在这个屡战屡败、屡败屡战的过程中,他们积累了大量实验经验,这为后续工作奠定了坚实基础。

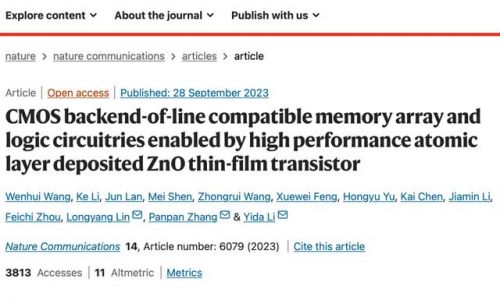

最终,相关论文以《基于高性能原子层沉积 ZnO 薄膜晶体管的 CMOS 后端兼容存储器阵列和逻辑电路》(CMOS Backend-of-Line Compatible Memory Array and Logic Circuitries Enabled by High Performance Atomic Layer Deposited ZnO Thin-film Transistor)为题发在 Nature Communications[1]。

南方科技大学博士生王文辉是第一作者,李毅达、北京邮电大学特聘研究员张盼盼、南方科技大学助理教授林龙扬担任共同通讯作者。

图 | 相关论文(来源:Nature Communications)

“此外,这篇论文也得到了期刊编辑的赞赏,被 feature 在期刊的 device(器件)页面上 [2]。”李毅达说。

曾在台积电工作,深谙科研和产业的转移和贯通

下一步,他们将研究更加复杂的氧化物半导体集成电路设计,例如加法器、乘法器、微型处理器等。同时,计划将氧化物晶体管的特征尺寸推进至纳米级别,为氧化物半导体在产业界的应用开辟道路。

如前所述,李毅达是在新加坡出生的新加坡公民。此前,他在新加坡国立大学完成了学士学位和博士学位。

加入南方科技大学之前,他在业界和学界都有一定的工作经验。加入南方科技大学之前,他曾在台积电工作。

对此他表示:“这段经历让我理解了微电子科研和微电子产业的不同,也让我理解了科研和产业的转移和贯通。”

另外,业界、学界的研究方法和工作方式可谓非常不同:业界侧重于通过不懈努力促进研发效率;而学界侧重于通过偶然发现来促进更多创新和创造。

“将这两种不同的研究方法和工作方式融会贯通到我们课题组,就可以持续产出好的成果。我认为这两个方面也能构成科研的支柱,我相信同行也都认同这一点。”他说。

而之所以选择来到中国发展,是因为这里能提供合适的机会和条件。同时,李毅达的专业知识和技能也符合中国目前发展微电子产业的需要,同时中国也能提供给他施展拳脚的平台和资源。

“所以,无论是从事尖端微电子研究的愿景,还是可以为我科研工作提供的支持和平台,南方科技大学都都能提供相对应的支持,我相信在这里可以进一步发展我的研究生涯,实现双赢。”他说。

参考资料:

1.Wang, W., Li, K., Lan, J.et al. CMOS backend-of-line compatible memory array and logic circuitries enabled by high performance atomic layer deposited ZnO thin-film transistor. Nat Commun 14, 6079 (2023). https://doi.org/10.1038/s41467-023-41868-5

2.https://www.nature.com/collections/bjiiabbacg

责任编辑:

文章来源:http://www.xinwulian.net/news/2023/1128/1755.shtml